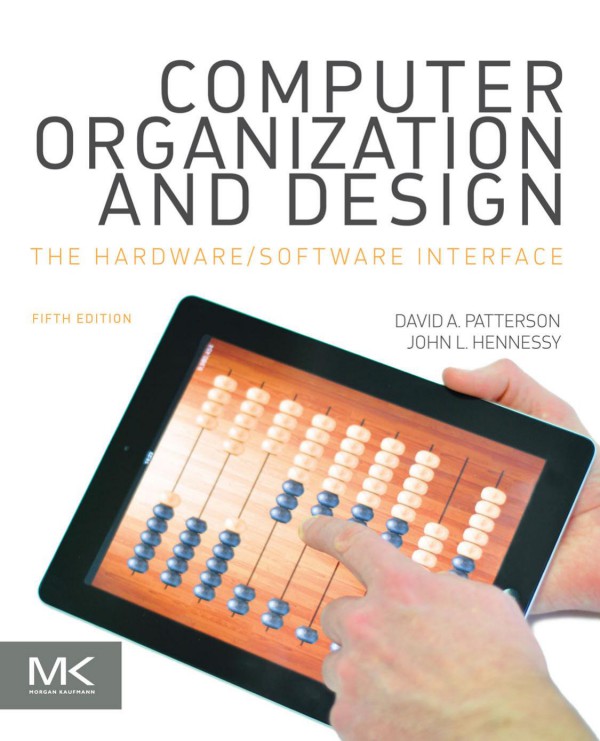

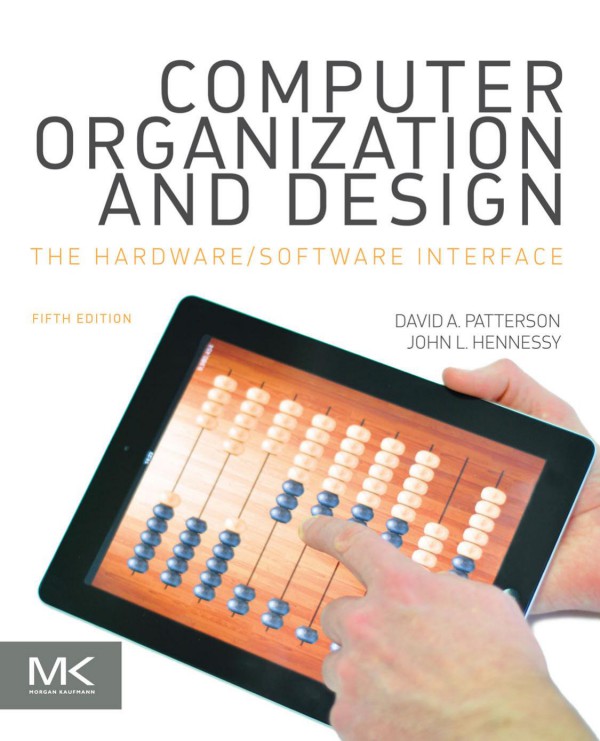

Computer Organization and Design The Hardware Software Interface 5th Edition by David A Patterson, John L Hennessy ISBN 0124077269 9780124077263

Original price was: $50.00.$25.00Current price is: $25.00.

Authors:David A. Patterson; John L. Hennessy , Series:Cyber Security [58] , Tags:Computers; Systems Architecture; General; Microprocessors; Computer Engineering; Computer Organization and Design: The Hardware/Software Interface; Fifth Edition (2014) 793pp. 978-0-12-407726-3 , Author sort:Patterson, David A. & Hennessy, John L. , Ids:Google; 9780124077263 , Languages:Languages:eng , Published:Published:Apr 2013 , Publisher:Morgan Kaufmann , Comments:Comments:The fifth edition of Computer Organization and Design-winner of a 2014 Textbook Excellence Award (Texty) from The Text and Academic Authors Association-moves forward into the post-PC era with new examples, exercises, and material highlighting the emergence of mobile computing and the cloud. This generational change is emphasized and explored with updated content featuring tablet computers, cloud infrastructure, and the ARM (mobile computing devices) and x86 (cloud computing) architectures. Because an understanding of modern hardware is essential to achieving good performance and energy efficiency, this edition adds a new concrete example, “Going Faster,” used throughout the text to demonstrate extremely effective optimization techniques. Also new to this edition is discussion of the “Eight Great Ideas” of computer architecture. As with previous editions, a MIPS processor is the core used to present the fundamentals of hardware technologies, assembly language, computer arithmetic, pipelining, memory hierarchies and I/O. Instructors looking for fourth edition teaching materials should e-mail [email protected]. Winner of a 2014 Texty Award from the Text and Academic Authors AssociationIncludes new examples, exercises, and material highlighting the emergence of mobile computing and the cloudCovers parallelism in depth with examples and content highlighting parallel hardware and software topics Features the Intel Core i7, ARM Cortex-A8 and NVIDIA Fermi GPU as real-world examples throughout the book Adds a new concrete example, “Going Faster,” to demonstrate how understanding hardware can inspire software optimizations that improve performance by 200 timesDiscusses and highlights the “Eight Great Ideas” of computer architecture:Â Performance via Parallelism; Performance via Pipelining; Performance via Prediction; Design for Moore’s Law; Hierarchy of Memories; Abstraction to Simplify Design; Make the Common Case Fast;Â and Dependability via RedundancyIncludes a full set of updated and improved exercises