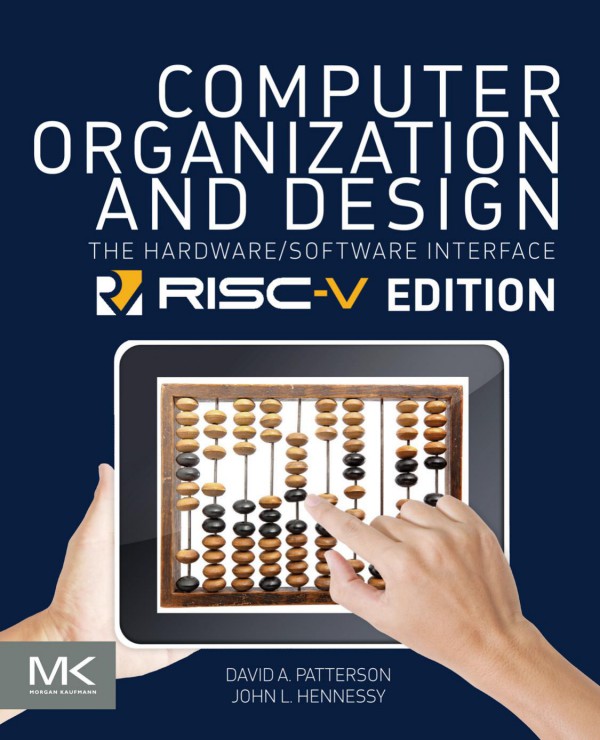

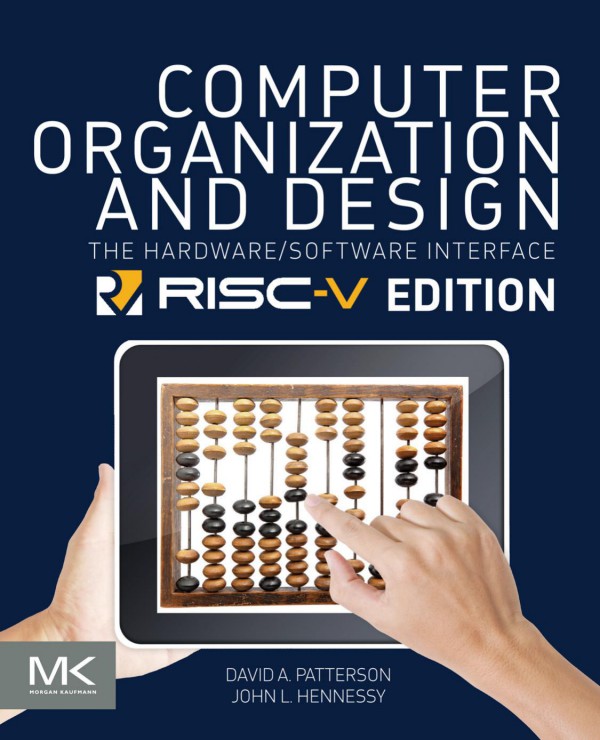

Computer Organization and Design RISC V Edition The Hardware Software Interface 1st Edition by David A Patterson, John L Hennessy ISBN 0128122757 9780128122754

Original price was: $50.00.$25.00Current price is: $25.00.

Authors:David Patterson; John L. Hennessy , Series:IT & Computer [312] , Tags:Computers; Computer Architecture; Computer Organization and Design: The Hardware/Software Interface , Author sort:Patterson, David & Hennessy, John L. , Ids:9780128122754 , Languages:Languages:eng , Published:Published:Apr 2017 , Publisher:Elsevier Science , Comments:Comments:The new RISC-V Edition of Computer Organization and Design features the RISC-V open source instruction set architecture, the first open source architecture designed to be used in modern computing environments such as cloud computing, mobile devices, and other embedded systems. With the post-PC era now upon us, Computer Organization and Design moves forward to explore this generational change with examples, exercises, and material highlighting the emergence of mobile computing and the Cloud. Updated content featuring tablet computers, Cloud infrastructure, and the x86 (cloud computing) and ARM (mobile computing devices) architectures is included. An online companion Web site provides advanced content for further study, appendices, glossary, references, and recommended reading. Features RISC-V, the first such architecture designed to be used in modern computing environments, such as cloud computing, mobile devices, and other embedded systems Includes relevant examples, exercises, and material highlighting the emergence of mobile computing and the cloud